국내 연구팀, 초저온·초고속 고품질 그래핀 제조 기술 개발

- 김종서 기자

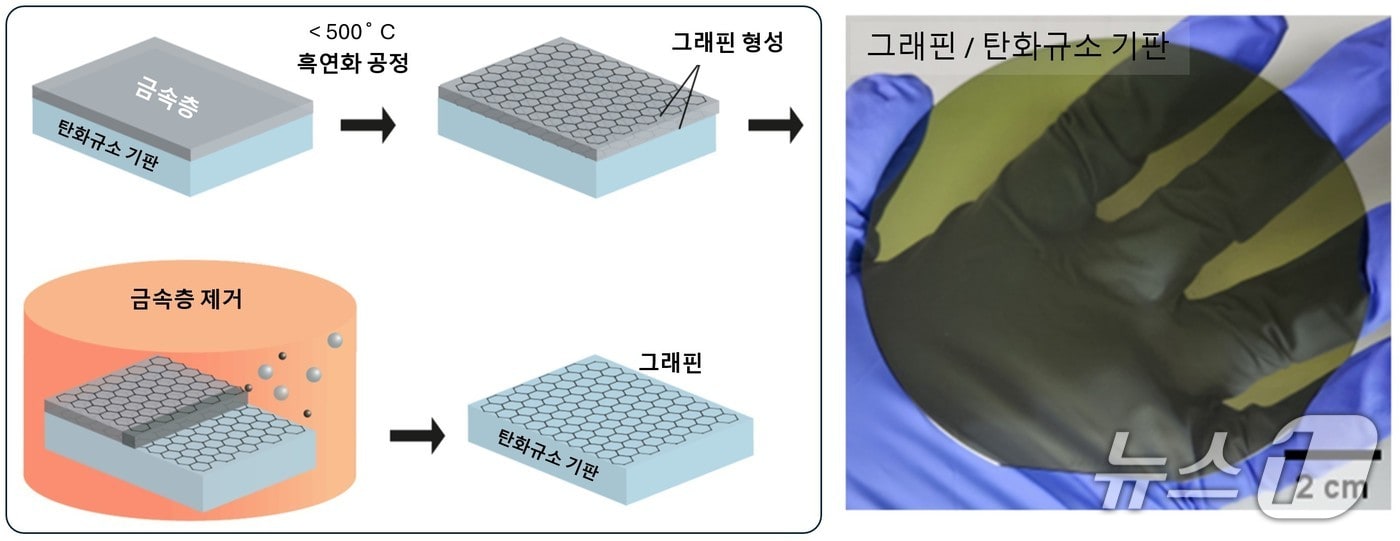

(대전=뉴스1) 김종서 기자 = 반도체 공정에서 1500도이상의 화덕이 반드시 필요했던 그래핀 제조가 단 500도 이하의 짧은 공정으로 가능해졌다.

한국연구재단은 연세대 금현성 교수, 경북대 이태훈·박홍식 교수, 세종대 김성규 교수 연구팀이 실리콘카바이드(SiC) 기판 위에 고품질 그래핀을 초저온·초고속으로 만드는 기술을 개발하고 이를 바탕으로 질화갈륨(GaN)·질화알루미늄(AlN) 같은 차세대 반도체 박막 제조를 성공적으로 실증했다고 1일 밝혔다.

최근 전력반도체, 고주파 소자, 마이크로 LED 분야에서 고성능 질화물(GaN·AlN) 반도체 수요가 빠르게 증가하고 있다. 질화물 반도체를 기판에서 쉽게 떼어낼 수 있는 최적의 기판을 만들기 위해서는 SiC 기판을 1500도 이상의 고온에서 그래핀화하는 공정이 필요하다.

이런 초고온 공정은 SiC 기판 표면을 거칠게 만들고 그래핀 두께도 불균일해지며 고가의 SiC 기판을 재사용하기 어려워 산업 확장을 위한 제조공정의 변화가 필요했다.

연구팀은 500도 이하의 낮은 온도에서 기판 표면 손상 없이 단결정에 가까운 고품질 그래핀을 만드는 데 성공했다.

저온 공정을 가능케 한 핵심 물질은 니켈(Ni) 금속이다. 연구팀은 탄소가 그래핀 형태로 재배열될 때 니켈을 금속 촉매로 도입하면 에너지가 안정되는 조건을 만들어 준다는 사실을 발견했다.

이를 바탕으로 Ni 두께와 온도를 조절해 320도에서는 단층~2층 그래핀, 500도에서는 다층 그래핀이 모두 몇 초 안에 형성됨을 확인했다.

이런 저온 공정 덕분에 SiC 기판 표면이 거칠어지지 않고 원자 단위로 매끈한 상태를 그대로 유지함으로써 최종 반도체 박막은 고온 기반 공정보다 매우 높은 결정성을 보였다.

또 주목할 점은 저온 공정이 필수였던 차세대 반도체 기술인 2D 기반 에피택시(방향성을 가진 단결정 박막을 성장시키는 반도체 기술) 방식이 가능해졌다는 점이다.

이는 고가의 SiC 기판 재사용과 이종소재 집적이 가능하다는 의미다. 연구팀은 저온 공정으로 제작된 반도체 박막을 마치 스티커 떼듯이 기판에서 깨끗이 떼어내는 데에도 성공했다.

금 교수는 "그래핀 제조 기술을 저온으로 내리면서 기판 재사용 문제와 제조비 절감에 해법을 제시한 연구"라며 "향후 저온 기반 2D 재료 합성 및 이종 에피택시 연구의 중요한 이론적 근거가 될 것으로 예상된다"고 말했다.

이번 연구 성과는 국제학술지 '사이언스 어드밴시스(Science Advances)'에 온라인 게재됐다.

jongseo12@news1.kr

Copyright ⓒ 뉴스1. All rights reserved. 무단 전재 및 재배포, AI학습 이용금지.