|

| 사진 왼쪽은 기존 시스템반도체의 평면 설계. 오른쪽은 삼성전자의 3차원 적층 기술 'X-Cube'를 적용한 시스템반도체의 설계. (삼성전자 제공) 2020.8.13/뉴스1 |

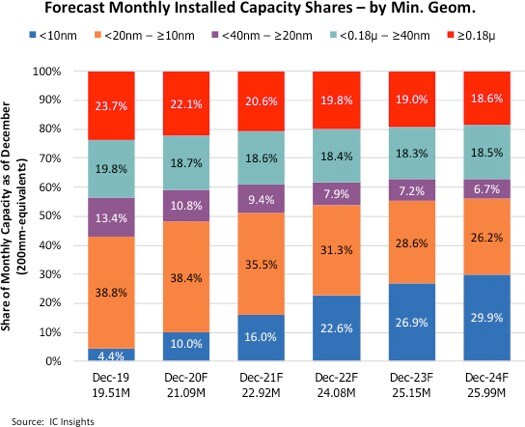

반도체 생산에서 10나노미터 이하의 첨단미세공정 비중이 2024년 현재의 3배로 늘어날 것이라는 전망이 나왔다. 미세 공정 개발과 양산 경쟁이 치열해질 것으로 보인다. 19일 업계에 따르면 반도체 전문 시장조사기관 IC인사이츠는 "2020년 전체 웨이퍼 캐파에서 10㎚(나노미터·10억분의 1m) 공정이 차지하는 비중이 10%에서 오는 2024년에는 30%까지 증가할 것"이라며 이같이 전망했다.

IC인사이츠는 "2022년 처음으로 10나노 이하 공정이 20% 이상의 비중을 갖게 될 것"이라고 덧붙였다.

보고서에 따르면 2020년 현재 모든 웨이퍼 캐파의 48%가 20나노 이하대에서 운용중이다. 그중 10㎚미만은 10.0%, 10나노 이상 20나노 이하 공정이 38.4%다.

웨이퍼 캐파(웨이퍼 생산량)란 공장설비가 100% 가동된다고 가정했을 때 동시에 투입돼 반도체 생산이 가능한 웨이퍼의 양을 의미한다. IC인사이츠에 따르면 현재 10나노 이하 공정을 이용해 팹을 운영하고 있는 제조사는 삼성전자와 대만의 TSMC 그리고 인텔뿐이다. 한국의 주력 산업인 D램과 낸드플래시 등 메모리 반도체분야에서는 10나노대 초중반 공정이 최신 공정으로 10나노 이하는 시스템 반도체를 생산하는 파운드리 업계에서 공정개발과 양산이 진행 중이다.

10나노 이하의 초미세공정은 더 빠른 속도, 더 낮은 전력 소비, 더 낮은 단위 면적당 비용 등의 이점이 많지만 그만큼 설계와 공정개발 양산이 쉽지 않다.

블룸버그 통신에 따르면 박재홍 삼성전자 파운드리 사업부 부사장은 최근 협력사 개발자들과 기술 동향을 공유하는 한 행사에서 "2022년까지 3㎚(나노미터·10억분의 1m) 양산에 들어갈 것"이라고 밝힌 바 있다. TSMC도 2022년 하반기 3나노미터, 2024년 2나노미터 반도체 생산을 하겠다고 포부를 드러낸 바 있다.

반도체 업계 관계자는 "초미세 공정의 비중이 올라간다는 것은 결국 10나노 이하 미세 공정도 세분화되고 한 자릿수 후반대 공정은 경쟁에서 밀릴 수도 있다"면서 "결국은 미세 공정 개발과 양산의 경쟁에 반도체 산업의 명운이 걸려 있다는 것"이라고 설명했다.

|

| 공정별 웨이퍼 생산량 변화 전망 추이(자료=IC인사이츠)2020.11.18/뉴스1 © 뉴스1 |

inubica@news1.kr

![블랙핑크 로제, 미니드레스로 섹시미 과시…화려한 금발도 눈길 [N샷]](https://image.news1.kr/system/photos/2024/4/16/6598509/no_water.jpg/dims/resize/276/crop/276x184/thumbnail/138x92!/optimize)

![뉴진스 다니엘, 소파 위 도발 눈빛...탄탄 복근까지 [N화보]](https://image.news1.kr/system/photos/2024/4/16/6599923/no_water.jpg/dims/resize/276/crop/276x184/thumbnail/138x92!/optimize)

![뉴진스 해린, 명품 화보서 독보적 미모...우아한 '고양이상' [N화보]](https://image.news1.kr/system/photos/2024/4/12/6594071/no_water.jpg/dims/resize/276/crop/276x184/thumbnail/138x92!/optimize)